### **Timing Hazards**

Do to timing delays, the <u>transient behavior</u> of a logic circuit may differ from what is predicted by a <u>steady-state</u> analysis. A circuit's output may produce a glitch at a time when steady-state analysis predicted that the output should not change. A hazard exist when a circuit has the possibility of producing a glitch.

Types of Hazards...

- ►Static 1 Hazard

- ►Static 0 Hazard

- **▶**Dynamic Hazard

Computer Engineering Technology

$R \cdot I \cdot T$

G. H. Zion

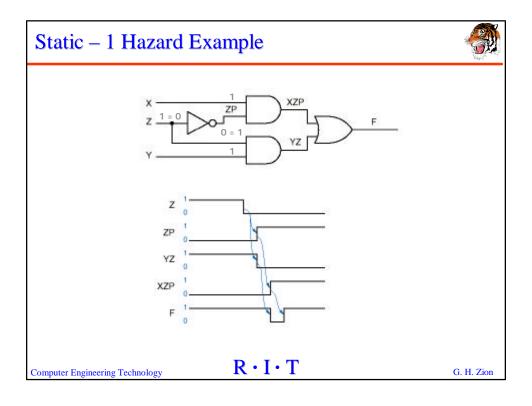

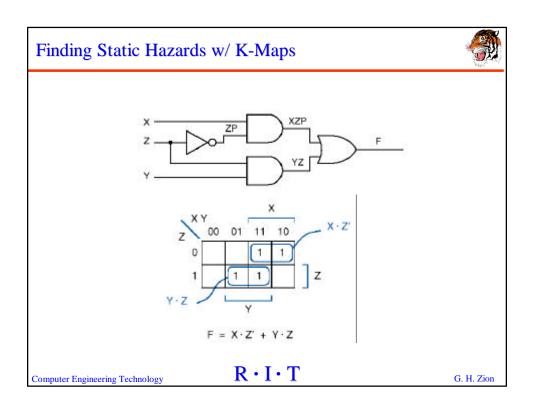

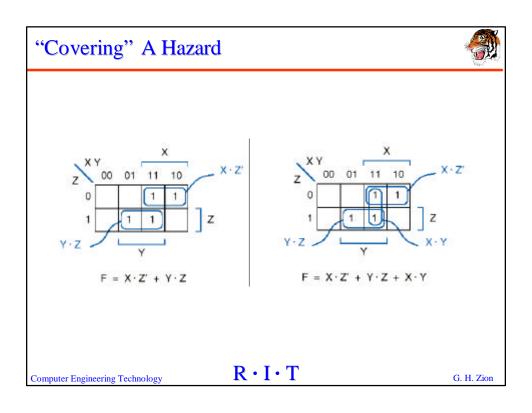

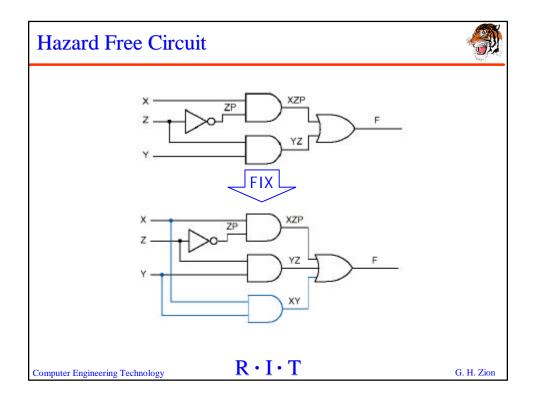

#### Static - One Hazard

A static-1 hazard is a pair of input combinations that : (a) differ in only one input variable and (b) both give a give a 1 output; such that it is possible for a momentary 0 output to occur during a transition in the differing input variable.

Computer Engineering Technology

$R \cdot I \cdot T$

G. H. Zion

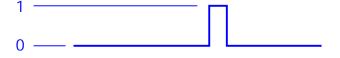

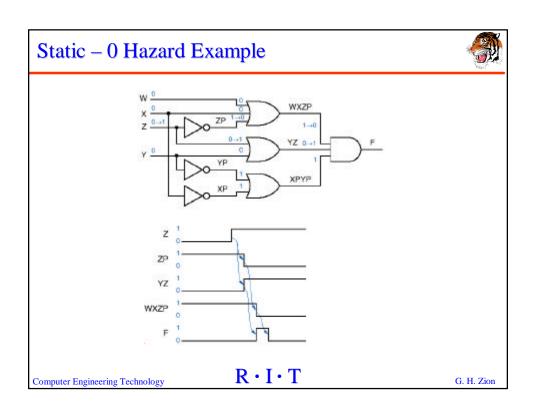

### Static - Zero Hazard

A static-0 hazard is a pair of input combinations that : (a) differ in only one input variable and (b) both give a give a 0 output; such that it is possible for a momentary 1 output to occur during a transition in the differing input variable.

Computer Engineering Technology

$R \cdot I \cdot T$

G. H. Zion

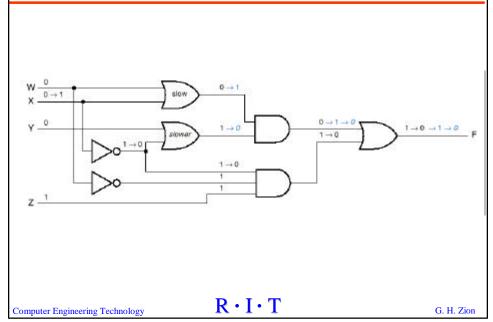

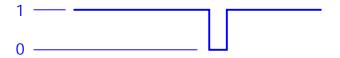

## Dynamic Hazard

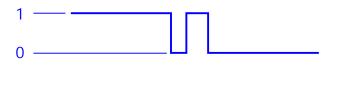

A dynamic hazard is the possibility of an output changing more than once as the result of a single input transition. A dynamic hazard can occur if there are multiple paths with different delays from the changing input to the changing output

Computer Engineering Technology

$R \cdot I \cdot T$

G. H. Zion

# **Dynamic Hazard Example**